# **42nd EOS/ESD SYMPOSIUM AND EXHIBITS**

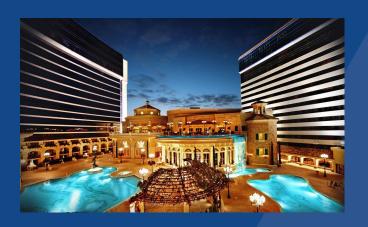

September 13-18, 2020 Peppermill Resort and Casino 2707 S Virginia St, Reno, NV 89502

# **EXPLORE.**

Technical Sessions Tutorials Manufacturing Track Workshops

# INNOVATE.

Featured Keynote

Hands-on Demonstrations

Invited Talks

Year-in-Review

IoT Workshop

# NETWORK.

Industry Professionals Social Receptions Contests Exhibition

# Welcome

Dear EOS/ESD colleagues,

On behalf of EOS/ESD Association, Inc. and the 2020 Symposium Steering Committee, it is my honor to welcome you to the 42nd Annual EOS/ESD Symposium and Exhibits at the Peppermill Resort & Casino, in Reno, Nevada. The EOS/ESD Symposium represents the world's leading forum on electrostatic discharge and overstress. The 42nd Symposium awaits you with a dense program packed with a keynote, two year-in-review presentations, tutorials, exhibits, workshops, technical sessions, and invited talks.

This year a new special session dedicated to the relationships and interactions between ESD and EMC will be organized in collaboration with EMC Society. This special session will be held on Wednesday, including four invited papers in the morning and 5 short tutorials in the afternoon. The special session will be then concluded by a panel discussion with experts from ESD Association and EMC society.

This year the structure of the Symposium is changing with two separate and dedicated parallel events for manufacturing and IoT. The Manufacturing Conference will offer technical sessions, technology showcases, hands-on sessions, workshops, and a panel discussion. The Workshop on Robustness of IoT Devices will offer unique industry-wide IoT expert invited speakers and peer presentations with that will cover the numerous challenges of meeting reliability and robustness requirements. Here is a brief overview of the highlights of the Symposium:

World-class experts, in all areas of EOS and ESD, will present 33 tutorials offered around the Symposium, on Sunday, Monday, and Thursday. In addition to classics on Advanced on-chip Protection, ESD Circuits, and TCAD Fundamentals, we have an increasing focus on System Level Protection, and Electrical Overstress (EOS). New tutorials include System Level ESD/EMI: Principles, Design Troubleshooting, & Demonstrations. Many previously offered tutorials have been refreshed with updated material, including ESD Controls for CDM and Ultra-Sensitive Devices and Circuit Boards.

Our industry exhibits display a wide variety of ESD solutions from established products to leading-edge innovations. Representatives from over 40 different companies welcome you to introduce their products and services with the help of short presentations and live demonstrations. The exhibition starts in the exhibit hall during the welcome reception on Monday evening and continues until Wednesday afternoon. The exhibitors are one of the cornerstones of the symposium, and they offer a unique opportunity for face-to-face discussions with professionals and hands-on experience on static control methods, evaluation techniques, ESD testing hardware, and many other ESD solutions. You can even bring your samples to find out whether a particular solution works for you.

In the technical sessions we will have 26 peer-reviewed technical papers and seven invited technical papers. These will be presented from Tuesday through Thursday in 12 sessions covering current research topics in the areas of advanced CMOS, RF/HV/MEMS, system-level ESD/modeling/soft failures, ESD transient analysis, ESD case studies, EOS/ESD EDA tools, numerical modeling, and ESD testing. The papers are presented by experts from industry and academia driving leading edge research and development. In addition, this year there will be also two special poster sessions, including both published and open posters. During these sessions we will have the privilege to host also invited contributions coming from IEW and IRPS.

Four symposium workshops and two panel discussions, which take place on Tuesday and Wednesday evenings, offer an interactive forum for sharing experiences, exchanging knowledge, and exploring potential solutions. The topics cover a wide range from ESD verification tools, latch-up testing, process assessment, and esd education in the field. Each workshop allows participants the opportunity to learn different perspectives from other colleagues in the field to discuss sometimes controversial topics in an informal environment. The two panel discussions will have active involvement of the experts from the special EMC session and the IoT workshop.

I most warmly invite every one of you to the General Chair's Reception on Wednesday September 16 from 7:00 PM to 9:00 PM.

The EOS/ESD Symposium is the premier international event for professionals in industry and academia to meet their peers and learn about the latest technical findings and innovative designs. Come, learn, and have fun! Sincerely,

Lorenzo Cerati, STMicroelectronics 2020 EOS/ESD Symposium General Chair

# Table of Contents

| Registration, Fees, Hours                        | 4    |

|--------------------------------------------------|------|

| General Information                              | 4    |

| Welcome Reception                                | 4    |

| Annual Meeting and Awards Breakfast              | 4    |

| Professional and Technical Women's Reception     | 4    |

| General Chair's Reception                        | 4    |

| Invited Breakfast University Students/Professors | 4    |

| First Time Attendee Social Hour                  | 4    |

| Schedule                                         | 5-7  |

| Keynote                                          | 8    |

| Professional Certification                       | 9    |

| Tutorials1                                       | 0-24 |

| Technical Sessions2                              | 5-35 |

| Workshops3                                       | 6-37 |

| Exhibits                                         | 38   |

| ESDA Officers, Board of Directors, and HQ Staff. | 39   |

| Steering Committee                               | 39   |

| Technical Program Committee                      | 40   |

| Hotel Reservations & Information                 | 41   |

| Registration Form4                               | 2-43 |

| Upcoming Announcements4                          | 4-45 |

## **On-Site Registration Hours**

Registration will be open at the following times:

| Sunday, September 13    | 7:30 a.m 5:00 p.m. |

|-------------------------|--------------------|

| Monday, September 14    | 7:30 a.m 5:00 p.m. |

| Tuesday, September 15   | 7:30 a.m 5:00 p.m. |

| Wednesday, September 16 | 7:30 a.m 5:00 p.m. |

| Thursday, September 17  | 7:30 a.m 5:00 p.m. |

### Symposium \$600

(Includes technical sessions, workshops, and exhibits) Bonus: Includes 30 days On-Demand access\*

#### **Tutorials \$510**

(Sunday, Monday, OR Thursday (Full Day)) Mix and Match On-Site and On-Demand tutorials

### **Bundled Fees \$1,765**

(Symposium plus Sun., Mon., and Thurs. full tutorial days) Mix and Match On-Site and On-Demand tutorials Bonus: Includes 30 days On-Demand access\*

# ESD Program Development and Assessment (ANSI/ESD S20.20) \$1,510

(Attendance limited to first 20 registrants)

This seminar is not included in the bundled fee.

You will receive a complimentary 2021 membership with your **On-Site** Symposium registration which will allow you to enjoy the full benefits of membership in 2021.

#### **Student Fees**

EOS/ESD Association, Inc., offers a fifty percent discount and waived fees to all Symposium tutorials for full-time students (first author only). Proof of enrollment required. Student fees apply only to on-site symposium and tutorial registration and do not apply to bundled fees, ANSI/ESD S20.20 two day tutorial, live stream, on-demand.

# **General Information**

#### **Symposium Proceedings**

Each paid registrant receives one electronic copy of the proceedings.

# General Information continued

## **Hospitality Suites**

To maintain the objectives of the Symposium, EOS/ESD Association, Inc. encourages all exhibitors and guest organizations to schedule their hospitality and other social events at times that do not conflict with the Symposium presentations and educational activities.

### **Age Limits**

No one under 18 years of age will be admitted to the exhibit hall.

#### **Unauthorized Solicitation**

Solicitation of business on the premises during the EOS/ESD Symposium by manufacturers or others who are not participating as exhibitors is prohibited.

## Recording

Video and/or audio recording of Symposium events is prohibited without the prior written authorization of EOS/ESD Association, Inc.

## **Welcome Reception**

A welcome reception for all attendees will be held on Monday, September 14, at 6:00 p.m. in the exhibit hall. Network with your colleagues, share your ESD work experiences with others, view the exhibits, or simply pass the time meeting new people and making new friends. The 2020 Steering Committee will greet you and answer any questions regarding the Symposium.

## **Annual Meetings and Awards Breakfast**

The annual meeting and awards breakfast for all registered attendees and exhibitors will be held Tuesday, September 15, at 7:30 a.m. Following breakfast, General Chair, Lorenzo Cerati, will officially open the Symposium. Vice General Chair, Wolfgang Stadler, will present the 2019 EOS/ESD Symposium paper awards. Technical Program Chair, Souvick Mitra, will cover highlights of the 2020 technical program. Association President, Alan Righter, will present the Association's annual report. Awards Chair, Charvaka Duvvury, will present the 2020 Association awards.

#### **Professional and Technical Women's Reception**

The Professional and Technical Women's Reception provides a friendly environment where women in the field of ESD can network and share work experiences. This year's reception will be held on Monday, September 14, from 5:00 p.m. to 6:00 p.m.

# University Students/Professors Invited to Wednesday Breakfast with ESDA Management

Wednesday, September 16, 7:00 a.m-8:00 a.m.

#### **First Time Attendee Social Hour**

Wednesday, September 16, 12:30 p.m.-1:00 p.m.

## Young Professionals Social Reception

Wednesday, September 16, 1:00 p.m.-1:30 p.m.

# **General Chair's Reception**

Lorenzo Cerati invites attendees and exhibitors to the general chair's reception on Wednesday, September 16, from 7:00 pm to 9:00 pm. **Poster presentations of technical papers from all sessions will be on display.** Don't miss this opportunity to network and share informal conversation with authors, industry professionals, and peers.

#### **SUNDAY, SEPTEMBER 13, 2020**

Registration 7:30 a.m. - 5:00 p.m.

Tutorials 8:30 a.m. - 4:30 p.m. FC100: ESD Basics for the Program Manager

8:30 a.m. - 12:00 p.m. DD150: Introduction to RF ESD Design

1:00 p.m. - 4:30 p.m DD300: Circuit-Level Modeling and Simulation of On-Chip Protection (DD)

#### **MONDAY, SEPTEMBER 14, 2020**

Registration 7:30 a.m. - 5:00 p.m.

Tutorials 8:30 a.m. - 4:30 p.m. FC101: How To's of In-Plant ESD Auditing and Evaluation Measurements (PrM)

8:30 a.m. - 12:00 p.m. DD340: Integrated ESD Device and Board Level Design

1:00 p.m. - 4:30 p.m. DD214: Latchup Physics and Prevention NEW 5:00 p.m. - 6:00 p.m. Professional and Technical Women's Reception

Welcome Reception 6:00 p.m. - 9:00 p.m. Exhibits Open

### **TUESDAY, SEPTEMBER 15, 2020**

Registration 7:30 a.m. - 5:00 p.m.

Reception

Awards Breakfast 7:30 a.m. - 9:00 a.m. Annual Meeting and Awards Breakfast

S20.20 8:00 a.m. - 5:00 p.m. FC340: ESD Program Development and Assessment (ANSI/ESD S20.20) (PrM) (Day 1)

Keynote 9:00 a.m. - 9:45 a.m. Coming soon

Exhibits Open 9:30 a.m. - 5:30 p.m.

Technical Sessions 10:15 a.m.-10:25 a.m. Exhibitor Showcase in Session 1A and 1B

10:25 a.m.-12:05 p.m. 1A: Advanced CMOS EOS/ESD and Latchup

10:25 a.m.-12:05 p.m. 1B: Device Testing: Testers, Methods and Correlation Issues I

1:15 p.m. - 1:25 p.m. Exhibitor Showcase in Sessions 2A and 2B

1:25 p.m. - 2:15 p.m. 2A: Numerical Modeling and Electronic Design Automation I 1:25 p.m. - 2:15 p.m. 2B: Device Testing: Testers, Methods and Correlation Issues II

3:00 p.m. - 3:10 p.m. Exhibitor Showcase in Sessions 3A and 3B

3:10 p.m. - 4:00 p.m.

3A: Numerical Modeling and Electronic Design Automation II

3:10 p.m. - 4:25 p.m.

3B: Device Testing: Testers, Methods and Correlation Issues III

Workshops A 5:10 p.m. - 6:25 p.m. A.1 ESD Verification Tools: Are We There Yet?

A.2 Finding the Step Where ESD failure Occurs in Manufacturing - Process Assessment Meets Event

Detection

#### TUESDAY, MANUFACTURING

Welcome 7:30 a.m. - 9:00 a.m. Awards Breakfast

9:00 a.m. - 9:45 a.m. Keynote: ESD Control Program Management for the Factory of Tomorrow

Technical Sessions 10:15 a.m. - 11:30 a.m. Manufacturing 1

1:00 p.m. - 1:30 p.m. Technology Showcase 1 - StaticStop/SelecTech, Inc.

1:30 p.m. - 2:00 p.m. Technology Showcase 2 - Core Insight, Inc.

2:25 p.m. - 3:25 p.m. Panel Session

Important Notice: Due to global events some presenters will appear via live stream, or through a prerecorded presentation. Some presenters will appear virtually for a live Q&A. A technical expert will be present for Q&A.

## **WEDNESDAY, SEPTEMBER 16, 2020**

| Invited Breakfast | 7:00 a.m 8:00 a.m.   | University Students/Professors Invited to Breakfast with ESDA Management      |

|-------------------|----------------------|-------------------------------------------------------------------------------|

| Registration      | 7:30 a.m 5:00 p.m.   |                                                                               |

| S20.20            | 8:00 a.m 5:00 p.m.   | FC340: ESD Program Development and Assessment (ANSI/ESD S20.20) (PrM) (Day 2) |

| Exhibits Open     | 8:30 a.m 1:30 p.m.   |                                                                               |

| Technical Session | s 8:00 a.m 8:40 a.m. | Year in Review: Electrical Overstress in Manufacturing and Test               |

|                   | 9:10 a.m 9:20 a.m.   | Exhibitor Showcase in Session 4A                                              |

|                   | 9:20 a.m 10:10 a.m.  | 4A: EOS/ESD Failure Analysis, Troubleshooting and Case Studies II             |

|                   | 9:10 a.m 9:20 a.m.   | Exhibitor Showcase in Session 4A                                              |

|                   | 9:20 a.m 10:10 a.m.  | EMC (Invited) I                                                               |

|                   | 10:35 a.m 11:25 a.m. | EMC (Invited) II                                                              |

|                   | 10:35 a.m 10:45 a.m. | Exhibitor Showcase in Session 5A                                              |

|                   | 10:45 a.m 11:35 a.m. | 5A: Numerical Modeling and Electronic Design Automation III                   |

| Reception         | 12:30 p.m 1:00 p.m.  | First Time Attendee Reception                                                 |

| Reception         | 1:00 p.m 1:30 p.m.   | Young Professionals Social Reception                                          |

|                   | 1:20 p.m 3:20 p.m.   | EMC Short Tutorials                                                           |

|                   | 1:20 p.m 2:00 p.m.   | Tutorial I. ESD Testing in accordance with IEC 61000-4-2                      |

|                   | 1:40 p.m 1:50 p.m.   | Exhibitor Showcase in Session 6A                                              |

|                   | 1:50 p.m 3:40 p.m.   | 6A: Published Posters                                                         |

|                   | 2:00 p.m 2:40 p.m.   | Tutorial II. System Level ESD Design Considerations and a Means of Evaluation |

|                   | 2:40 p.m 3:20 p.m.   | Tutorial III. Lessons-Learned in System-Level ESD Testing                     |

|                   | 3:40 p.m 4:20 p.m.   | Tutorial IV. System-Level ESD Failure Mechanisms and Mitigation Techniques    |

|                   | 4:20 p.m 5:00 p.m.   | Tutorial V. EMI Measurements in Manufacturing Environment                     |

| Workshops B       | 5:25 p.m 6:40 p.m.   | B.1 ESD Education in the Field B.2 EMC Expert Panel                           |

| Reception         | 7:00 p.m 9:00 p.m.   | General Chair's Reception Open to all Symposium Attendees and Exhibitors!     |

## WEDNESDAY, MANUFACTURING

| Technical Sessi | ions 8:00 a.m 8:50 a.m. | Manufacturing II                                                                                     |

|-----------------|-------------------------|------------------------------------------------------------------------------------------------------|

|                 | 9:15 a.m 9:45 a.m.      | Technology Showcase 3 - ORBIS Corporation                                                            |

|                 | 9:45 a.m 10:15 a.m.     | Technology Showcase Hands-On                                                                         |

| Workshop        | 10:45 a.m 12:00 p.m.    | Manufacturing Workshop - Assessment, Selection, and Qualification of Materials and Equipment Used in |

|                 |                         | the EPA                                                                                              |

## **THURSDAY, SEPTEMBER 17, 2020**

| IIIOICOD       | AI, OLI ILMBER I         | , <b>2020</b>                                                                        |

|----------------|--------------------------|--------------------------------------------------------------------------------------|

| Registration   | 7:30 a.m 5:00 p.m.       |                                                                                      |

|                | 8:00 a.m 8:40 a.m.       | Year in Review: ESD On-chip Design                                                   |

| Tutorials      | 8:30 a.m 12:00 p.m.      | FC391: Basics of ESD Process Assessment                                              |

|                | 8:30 a.m 12:00 p.m.      | DD/FC240: System Level ESD/EMI: Principles, Design Troubleshooting, & Demonstrations |

| Technical Sess | sions 8:55 a.m 9:05 a.m. | 8A: ESDA Standards Showcase                                                          |

|                | 9:05 a.m 10:20 a.m.      | 8A: System Level EOS/ESD/EMC                                                         |

|                | 10:45 a.m 12:25 p.m.     | 8A: System Level EOS/ESD/EMC (continued)                                             |

|                | 8:55 a.m 9:05 a.m.       | 8B: ESDA Advanced Topics Showcase                                                    |

|                | 9:05 a.m 10:20 a.m.      | 8B: Invited IRPS                                                                     |

|                | 10:45 a.m 12:00 p.m.     | 8B: Invited IRPS (continued)                                                         |

| Tutorials      | 1:00 p.m 4:30 p.m.       | FC121: Grounding - Variations, Concepts, Nuisances, Equipment & Troubleshooting      |

|                | 1:00 p.m 4:30 p.m.       | DD/FC130: System Level ESD/EMI: Testing to IEC and Other Standards (DD)              |

|                |                          |                                                                                      |

## FRIDAY, SEPTEMBER 18, 2020

8:00 a.m. - 5:00 p.m. Device Design Certification Exam 8:00 a.m. - 5:00 p.m. Program Manager Certification Exam

Important Notice: Due to global events some presenters will appear via live stream, or through a prerecorded presentation. Some presenters will appear virtually for a live Q&A. A technical expert will be present for Q&A.

Presenter: Dr.-Ing. Shahin Tajik

Florida Institute for Cybersecurity (FICS) Research

#### **EOS/ESD Association, Inc. Professional Certification**

EOS/ESD Association, Inc. offers professional certification for ESD control program managers and device design technical specialists.

#### **ESD Certified Professional-Program Manager**

The impact of the ANSI/ESD S20.20 ESD control program standard on the global industry has been extraordinary. As a result, EOS/ESD Association, Inc. recognizes the need to offer a certification program for individuals that are involved in designing, implementing, managing, and auditing ESD control programs in their facilities. The program manager certification program serves that purpose. In addition, the needs of the technical community for certification of various technical specialists are apparent.

Requirements for certification include attending required prerequisite tutorials and passing a final exam. All of the prerequisite courses cannot be completed by attending only the 2020 Symposium. Details of the certification program are also available at the registration desk.

The preferred tutorial sequence for the program manager curriculum is:

|    | COURSE TITLE                                                                   | FACE TO FACE TUTORIAL                         | ONLINE         |

|----|--------------------------------------------------------------------------------|-----------------------------------------------|----------------|

| 1  | FC100: ESD Basics for the Program Manager                                      | Symposium, Sunday, Sept. 13                   |                |

| 2  | FC101: How To's of In-Plant ESD Auditing and Evaluation Measurements           | Symposium, Monday, Sept. 14                   |                |

| 3  | FC110: Cleanroom Considerations for the Program Manager                        |                                               | Online Academy |

| 4  | FC120: Air Ionization Issues and Answers for the Program Manager               |                                               | Online Academy |

| 5  | FC200: Packaging Principles for the Program Manager                            |                                               | Online Academy |

| 6  | FC210: ESD Standards Overview for the Program Manager                          |                                               | Online Academy |

| 7  | FC140 - System Level for the Program Manager                                   |                                               | Online Academy |

| 8  | FC220: Device Technology and Failure Analysis for the Program Manager          |                                               | Online Academy |

| 9  | FC380: Electrostatic Calculations for the Program Manager and the ESD Engineer |                                               | Online Academy |

| 10 | FC340: ESD Program Development & Assessment (ANSI/ESD S20.20 Seminar)          | Symposium, Tuesday & Wednesday, Sept. 15 & 16 |                |

#### **ESD Certified Professional-Device Design**

ESD device design certification was developed for individuals that are involved in designing, testing, characterizing, and implementing improved ESD protection designs. Device design certification demonstrates knowledge, experience, and competency in the area of ESD design and test for device protection.

Requirements for certification include attending required prerequisite tutorials and passing a final exam. All of the prerequisite courses are not available in the 2020 Symposium tutorial program. Details of the certification program are also available at the registration desk.

The preferred tutorial sequence for the device design curriculum is:

|    | COURSE TITLE                                                                                             | FACE TO FACE TUTORIAL         | ONLINE         |

|----|----------------------------------------------------------------------------------------------------------|-------------------------------|----------------|

| 1  | DD110: ESD Basics for Advanced Protection Design                                                         |                               | Online Academy |

| 2  | DD301: SPICE-Based ESD Protection Design Utilizing Diodes and Active MOSFET Rail Clamp Circuits          |                               |                |

| 3  | DD211: EOS/ESD Failure Models and Mechanisms                                                             |                               |                |

| 4  | DD102: On-Chip ESD Protection in RF Technologies                                                         |                               | Online Academy |

| 5  | DD200: Charged Device Model Phenomena, Design, and Modeling                                              |                               | Online Academy |

| 6  | DD112: Latch-up Fundamentals                                                                             |                               | Online Academy |

| 7  | DD300: Circuit-Level Modeling and Simulation of On-Chip Protection                                       | Symposium, Sunday, Sept. 13   |                |

| 8  | DD302: Troubleshooting On-Chip ESD Failures                                                              |                               |                |

| 9  | DD120: Device TestingIC Component Level: HBM, CDM, MM, and TLP                                           |                               |                |

| 10 | DD311: Impact of Technology Scaling on ESD High Current Phenomena and Implications for Robust ESD Design |                               | Online Academy |

| 11 | DD220: Transmission Line Pulse (TLP) Basics and Applications                                             |                               | Online Academy |

| 12 | DD/FC130: System Level ESD/EMI: Testing to IEC and other Standards                                       | Symposium, Thursday, Sept. 17 | Online Academy |

#### **ESDA Certification Exams**

The certified professional program manager and device design exams will be held on Friday, September 18. To take the exam, applicants must have a registration form on file with EOS/ESD Association, Inc. headquarters complete with a \$50 filing fee prior to the Symposium.

## **TUTORIALS: SUNDAY, SEPTEMBER 13**

# FC100: ESD Basics for the Program Manager

8:30 a.m. - 4:30 p.m.

Ron Gibson, Advanced Static Control Consulting

Certification: PrM

#### **Abstract**

This tutorial provides the foundation material for understanding electrostatics and ESD and their role in the manufacturing and handling of ESD sensitive devices. The fundamental properties of charge, electric fields, voltage, capacitance, and current are discussed with a view towards understanding key electrostatic phenomena and electrical processes. These include charge gener ation and decay, material properties, and induction. An overview of device failure mechanisms is presented, including how these models impact ESD control programs. Finally, the course provides an overview of ESD control procedures during handling and manufacturing and an overview of ANSI/ESD S20.20 program requirements. This full day course is required for those in-plant auditors and program managers who are working toward professional ESD certification. The presentation includes many in-class demonstrations, videos, and animated slides.

Some sample topics covered in this course are:

- 1. Definitions and relationships among important electrical and mechanical properties

- 2. Causes of charge generation and decay

- 3. Field effects and voltages

- 4. Role of capacitance in ESD (Q=CV)

- 5. Overview of key measurements including common pitfalls of some measurements

- 6. Review of ESD failure models

- 7. Understanding and demonstrating electrostatic induction

- 8. Utility and limitations of air ionization

- 9. Basic goals of ESD controls

- 10. Properties of effective ESD control products and materials

- 11. Overview of ANSI/ESD S20.20 ESD program development requirements

#### **Learning Outcomes**

- An understanding of several concepts that are included in the ESD Program Manager Certification Exam.

- A deep understanding of ESD fundamentals that are vitally important for developing and managing sound ESD programs

- Students will learn effective techniques for demonstrating a wide range of ESD fundamentals

- Students will learn how to evaluate materials for CDM mitigation properties and much more

## **TUTORIALS: SUNDAY, SEPTEMBER 13**

# DD150: Introduction to RF ESD Design

8:30 a.m. - 12:00 p.m. Kathleen Muhonen, Qorvo

#### Abstract

This tutorial is an introduction to RF concepts and RF ESD clamp design. It is intended for ESD engineers who do not have an RF background to come up to speed on the concepts needed to design effective protection circuits. The RF concepts include impedance matching and smith chart basics. RF amplifier operation and load line basics are presented to give a foundation for the RF ESD protection circuit design. The tutorial will also touch briefly on RF switches and filters. The second half of the tutorial will focus on how to design an ESD clamp for an RF application. Concepts will be presented such as calculating the turn-on voltage of the clamp such that it will protect the part but not turn on during normal, RF operation. To design successful RF ESD clamps, concepts such as peakto-average power ratio will be explained for common cellular and WiFi standards. A clamp's parasitics also needs to be considered in an RF application so that the parasitics do not degrade the product's performance. Finally, some testing tools will be reviewed with respect to evaluating RF products. The challenges will be highlighted and different testing practices that are used in HBM, TLP and IEC testing of RF products will be reviewed.

#### **Learning Outcomes**

Learning outcomes are understanding of the following:

- Key RF and microwave concepts such as maximum power transfer, impedance matching and smith chart basics

- How components such as amplifiers, switches and LNA's have different metrics of performance for RF applications

- What RF parameters are needed to design a functional RF ESD clamp without RF performance degradation

- What to consider when determining the ESD robustness of an RF product

# DD300: Circuit-Level Modeling and Simulation of On-Chip Protection

1:00 p.m. - 4:30 p.m.

${\it Elyse \ Rosenbaum, \ University \ of \ Il lino is \ at \ Urbana-Champaign}$

Certification: DD

#### **Abstract**

This tutorial addresses modeling of on-chip ESD protection devices and simulation of ESD protection networks. The primary focus is SPICE-type simulation with compact (physics-based) models but a brief survey of other modeling approaches and simulation techniques will be provided. The physical operating principles of commonly-used ESD protection devices will be examined. The high-current characteristics and transient responses of those devices will be explored to ascertain what behaviors should be captured by a model intended for circuit-level simulation of ESD. Specific examples of model implementations will be provided. Techniques for circuit-level modeling of self-heating will be presented. Parameter extraction and model scalability will be addressed. This tutorial assumes some familiarity with device physics. It is directed toward persons with interests in semiconductor device physics, electronic design automation, and on-chip ESD protection circuit design.

#### **Learning Outcomes**

After completion of this tutorial, a student should know how to set up a netlist for simulation of an on-chip ESD protection networks. Students will have the necessary background to start developing their own compact models and will be familiar with resources for Verilog-A model development.

# **TUTORIALS: MONDAY, SEPTEMBER 14**

# FC101: How To's of In-Plant ESD Auditing and Evaluation Measurements

8:30 a.m. - 4:30 p.m.

Ron Gibson, Advanced Static Control Consulting

Certification: PrM

#### **Abstract**

Compliance verification is one of the most important elements of ESD program management and there are many technical and administrative pitfalls that can be avoided. The attendee will learn not only how to make valid auditing measurements in accordance with ESD TR53 - Compliance Verification of ESD Protective Equipment and Materials, but also how to rec ognize and avoid common pitfalls. Common instruments will be explained as well as the invalid test results that can result when they are used incorrectly. Advanced auditing techniques will also be covered that enable Class 0 devices to be handled successfully. There are many ways to administer effective compliance verification programs. Two successful examples will be presented that were developed independently by differ ent companies. Hidden administrative pitfalls that often result in poor compliance will also be discussed. This tutorial will be highly interactive with live demonstrations, in-plant photo graphs, and compelling video clips. Students will be encour aged to ask questions and to participate in the discussions.

#### **Learning Outcomes**

- -Understand auditing information included in ESD Program Manager Certification Exam

- -Learn to make and correctly interpret auditing measurements based on ESD TR 53

- -A deep understanding of five auditing options for sustaining program execution excellence

- -Understand the critical requirements to successfully handle extremely sensitive Class 0 devices

- -Develop real world solutions from the review of successful case studies and class discussions

# DD340: Integrated ESD Device and Board Level Design

8:30 a.m. - 12:00 p.m.

Harald Gossner, Intel Deutschland GmbH.

#### **Abstract**

The tutorial is a hands-on training course for performing a simulation based optimization of PCB ESD protection design and provides deep understanding of the relevant performance criteria both of TVS diodes and IO circuits. The presented method follows the system efficient ESD design (SEED) approach as recommended by the Industry Council on Target Levels and JEDEC. The method allows the achievement of correct first time PCB builds and reduces the respin effort for boards and ICs. Based on a TLP characterization of SoC interface circuits and TVS diodes, simulation models for impedance and clamping behavior, as well as failure threshold, are extracted. These are used to assess design solutions by transient simulations. This is showcased by real world examples.

#### Learning outcomes

The attendee will understand the concept of SEED simulation and will be able to apply it to an own PCB /IC codesign simulation. This will allow the system design attendee to run a pre-hardware optimization of the board protection and it will enable the IC protection engineer to evaluate his protection concept regarding the available design window for system ESD.

## TUTORIALS: MONDAY, SEPTEMBER 14

# **NEW DD214: Latchup Physics and**

## **Prevention**

1:00 p.m. - 4:30 p.m. Nathan Jack, Intel Corporation

#### Abstract

Latchup has occurred in CMOS technologies since their inception and continues as a threat in modern finFET technologies. This course will begin with a basic overview of the latchup phenomenon and then dig deeper into the theory and physics associated with it. Latchup mitigation techniques will be reviewed along with the physics behind them. These will include both design and process techniques. The basics and pitfalls of latchup testing will be taught, along with an introduction into transient latchup. Proper wafer-level test structure design and characterization will be taught.

The primary audience for this course is design and reliability engineers tasked with designing for latchup success. Latchup test engineers will also benefit from a deeper understanding of latchup physics and design practices. The course assumes some familiarity with basic circuit design practices and semiconductor physics. Participants will leave with a deeper understanding of the physics behind latchup, its mitigation, and the impact of future technology trends on latchup susceptibility.

### **Learning Outcomes**

- -- Understand the physics behind latchup

- -- Understand how technology scaling impacts latchup

- --Learn latchup mitigation strategies in design and process development and the physics behind them.

- --Will learn best practices for test structure creation and measurement and how to translate the results into latchup design rules.

- --Will understand the latchup test standard in the context of creating design rules to successfully pass the test as well as other real-world risks not covered by the standard.

# **TUTORIALS: TUESDAY & WEDNESDAY, SEPTEMBER 15-16**

# FC340: ESD Program Development and Assessment (ANSI/ESD S20.20)

8:00 a.m. - 5:00 p.m.

Ron Gibson, Advanced Static Control Consulting; John Kinnear, IBM Corporation

Certification: PrM

#### Abstract

This seminar provides instruction on designing and implementing an ESD control program based on ANSI/ESD S20.20. The course provides participants with the tools and techniques to prepare for an ESD facility audit. This two-day course is an ESDA certification requirement for in-plant auditors and program managers who are working toward professional ESD certification. The following topics are covered in this course:

- Overview of ANSI/ESD S20.20

- · How to approach an assessment

- Administrative elements

- ESD program assessment

- · ESD program techniques for different applications

- Technical elements

- · Overview of the assessment process

- The audit checklist and follow-up questions

It is recommended that the ESD Program Development and Assessment (ANSI S20.20) be taken after the certification candidate has taken most of the other program manager related tutorials.

# **TUTORIALS: THURSDAY, SEPTEMBER 17** FC391: Basics of ESD Process Assessment

8:30 a.m. - 12:00 p.m.

Wolfgang Stadler, Intel Deutschland GmbH.; Reinhold Gaertner, Infineon Technologies

#### Abstract

This tutorial gives an introduction to the approach and measurement methodologies for ESD process assessment and ESD risk analysis in typical production processes in semiconductor, printed-circuit board (PCB), and electronic system manufacturing industries. To large extents, the tutorial follows the ESD process assessment approaches described in ANSI/ESD Standard Practice SP17.1.

The tutorial summarizes the relevant physical parameters, for example, resistance, charge, electric fields, capacitances, resistances, discharge currents, and ESD event detection by EMI. The influence of these parameters on the ESD risks caused by charged personnel, charged devices and boards, and ungrounded conductors is discussed. Also, measurement techniques are explained in detail together with their limitations for the different process steps and strategies for an efficient ESD risk assessment. The application of those measurement techniques to assess possible ESD risks and to solve ESD problems are explained using theoretical and real-world case studies from many of the processes mentioned above. Examples of possible mitigation strategies are discussed with the attendees. The tutorial includes practical demonstrations and a hands-on session for the attendees to get experience and learn pitfalls of the most important measurement techniques used in ESD process assessment.

#### **Learning Outcomes**

The attendees will be enabled to analyze ESD critical process steps, select the appropriate measurement technique, and perform the measurement. They will learn how to evaluate the measurement results and assess the ESD risk in various typical process steps.

# DD/FC240: System Level ESD/EMI: Principles, Design Troubleshooting, & Demonstrations

8:30 a.m. - 12:00 p.m.

Jay Skolnik, Skolnik Technical Training

#### **Abstract**

System level ESD tutorial about how to reduce ESD effects on systems (boards, chassis, etc.). Real circuits will be demonstrated in class showing techniques to correct the detrimental effects. Theory and real-life examples from recent past will be used to substantiate the methods.

### **Learning Outcomes**

- •Understand how an ESD soft failure can upset a system and how to design to eliminate soft ESD failures

- •Realize how ESD and electrical noise can enter a system and acquire methods to locate / remove the issues from ESD and electrical noise based on electric & magnetic field edification

- •Encounter new methods to make a circuit board design more robust against direct ESD hits to a connector pin

- •Assess the Faraday Shield principle and learn to apply it directly to applications in order to reduce detrimental ESD/EMI effects

# **TUTORIALS: THURSDAY, SEPTEMBER 17** FC121: Grounding – Variations, Concepts, Nuisances, Equipment & Troubleshooting

1:00 p.m. - 4:30 p.m.

Jay Skolnik, Skolnik Technical Training

#### **Abstract**

Grounding for ESD control seems so simple, yet many times issues arise after a grounding strategy is implemented. This class will cover variations in grounding approaches, concepts to consider when employing a ground system, nuisances and how to troubleshoot them with the correct equipment.

#### **Learning Outcomes**

- Understand the term "ground" and all of its associated meanings from the industry in order to test, measure and/or design effective ground systems.

- Understand the various ESDA standards and test methods in regards to measuring ground connections.

- Realize the reason for a Common Point Ground and how to achieve it.

- Determine the right amount of resistance, (not too little and not too much) for many ESD control situations.

- Determine how to troubleshoot typical ground issues in order to maximize productivity.

# DD/FC130: System Level ESD/EMI: Testing to IEC and Other Standards

1:00 p.m. - 4:30 p.m.

Jeff Dunnihoo, Pragma Design, Inc.

Certification: DD

#### **Abstract**

This tutorial is intended to help those tasked with testing products to system level ESD standards by providing first an overview of how real-world system ESD events are simulated in different standards and testers in general, and then provide detailed information on IEC 61000-4-2, the most widely used standard. This introduction will highlight the similarities and differences between IEC, ANSI, Telcordia, and some automotive ESD standards. We will answer common questions regarding test setups, test points, and procedures, and address key issues, including: 1) differences between "verification" and "calibration" and when is each required; 2) test equipment requirements, the test environment, ground connections, return paths, and ground plane effects. 3) Testing procedures with demonstration on actual products, how the tester and procedure affects test results, and problems with test result variations due to simulator influences; 4) definitions of testing failure criteria for the product; 4) what points need to be tested and why, guidance on determining "operator accessible" points and ports, exempted points and ports, and what to do around connectors and connector pins. 5) ANSI and other ESD standards, the drive toward harmonization with IEC, the scope of different standards, and why they are unlikely to converge. This system level ESD tutorial will cover different perspectives on ESD as applied to electronic systems from the user's, the designer's, and even the designer's competitor's points of view.

## TUTORIALS: On-Demand 1 tutorial equals a half day credit

# DD200: Charged Device Model Phenomena, Design, and Modeling

On-Demand Tutorial

Michael Chaine, Micron Technology, Inc.; Melanie Etherton, NXP

Semiconductors

Certification: DD

#### **Abstract**

This course teaches basic ESD circuit design concepts and ideas required to design ESD protection for Charge Device Model ESD tests. The course covers a brief history of CDM ESD development, charge and discharge physics, characterization methods, CDM failures mechanisms, and CDM design-in strategies.

CDM ESD circuit design approaches and simulation setups for CDM failure debugging are presented in this tutorial on the basis of case studies. Insight into CDM circuit simulation requirements and physical aspects of the CDM ESD phenomenon that are important for reproducing the event with circuit simulation will be taught and modeling approaches for CDM specific device physical effects necessary for accurate circuit simulation will be introduced. This course also teaches methods for simplified CDM circuit simulations where detailed information is either not available or too complex to simulate.

The course focuses on what type of circuits fail during a CDM discharge event and teaches the different types of ESD design circuit strategies that can be applied to protect those circuits. This class covers basic to advanced topics for CDM ESD design, but the student is assumed to already have a basic understanding of the CDM test method.

#### **Learning Outcomes**

The attendees of this class are expected to have an improved understanding of the basics of charging of an IC component, CDM discharge event physical effects, internal circuit damages caused by the voltage and current during fast transient discharges and basic high current properties of ESD protection circuits in the CDM time domain. They should have an improved appreciation of circuit simulation methods for designing CDM ESD protection and for debugging failures caused by CDM ESD with circuit simulations. They should be able to apply ESD design strategies as discussed in the tutorial that have proven to protect ultra thin gate oxides of input circuitry and of devices connecting to signals that cross power domains techniques and strategies to protect cross domain circuits.

# **DD100: ESD Circuits**

On-Demand Tutorial

Eugene Worley, Silicon Crossing, LLC.

#### **Abstract**

This tutorial will focus on a number of clamp approaches including BigFETs or RC clamps, snap-back NFETs, diodes, SCRs including HV SCRs, low capacitance clamps methods including those for MOSFET based LNAs and RF transceiver switches, and cross domain clamping. Spice simulations and simple models where applicable will be used to design and analyze circuit performance. Models include HBM, CDM, and IEC sources, gate pull requirements for dynamically lowering snap-back thresholds, and diodes. Gate pull for snap-back NFETs will include cascade and stacked NFETs. The need for NQS MOSFET models will be discussed with respect to CDM simulations. Operational characteristics of diodes will be examined including simple models and turn on delay. Diode types to be examined include STI, gated, and gated with LDD block. Protecting RF transceiver switches will be studied and will include spice simulations and design of low capacitance snap-back NFETs. Cross domain analysis will feature SPICEbased gate oxide rupture models and design requirement for secondary clamps including secondary clamps for LNAs.

#### **Learning Outcomes**

The attendee will learn how to design BigFETs clamps, gate pull snap-back clamps, types of SCRs, and circuit protection networks. There will be an emphasis on circuit simulation for design and circuit models including failure mechanisms, tester models, pin interconnect parasitics, and diodes.

# TUTORIALS: On-Demand 1 tutorial equals a half day credit

# **DD240: ESD Device Qualification Testing**

On-Demand Tutorial

Brett Carn, Intel Corporation; Wolfgang Stadler, Intel Deutschland GmbH.

#### Abstract

This tutorial addresses the details of both Human Body Model (HBM) and Charged Device Model (CDM) qualification testing. This course will help in interpretation of the HBM joint standard JEDEC/ANSI/ESD JS-001-2014 including the following details: Waveform verification, understanding of Table 2A (minimum required set of pin combinations) and Table 2B (legacy pin combinations), pin categorization and pin grouping, I/O pin sampling, stress plans details including efficient testing (reduction in pin count) and some debugging options. In addition, this course will discuss CDM testing details regarding waveform verification, stress plans, peak current (Ipeak) variability and how does it affect the testing results, and debugging options as well as an overview on the new CDM joint standard JEDEC/ANSI/ESD JS-002-2014.

### **Learning Outcomes**

The attendee should come away with a stronger understanding of both human body model (ANSI/ESDA/JEDEC JS-001 - HBM) and charged device model (ANSI/ESDA/JEDEC JS-002 – CDM) testing specifications and the requirements called out in each of these specifications. For HBM this includes a better understanding of Table 2A and Table 2B and the use of association in Table 2A as well as opportunities to minimize test time and an understanding of cloned IO requirements. For CDM this includes a better understanding of the waveform verification requirements and the impacts of an air discharge on product qualification.

# DD311: Impact of Technology Scaling on Components High Current Phenomena and Implications for Robust ESD Design

On-Demand Tutorial

Gianluca Boselli, Texas Instruments

#### **Abstract**

This advanced tutorial will focus on high-current behavior of stand-alone components, with the aim of optimizing effectiveness of ESD clamp devices (irrespectively of their schematic implementation) and maximizing the ESD SOA (Safe Operating Area). Components in both Analog and Digital technologies will be discussed, with emphasis on technology trends. This class is intended for individuals who have taken the basic on-chip protection class and are familiar with the basic device physics for both ESD and latch-up.

### **Learning Outcomes**

- Understand the physics of basic components under high current conditions with particular emphasis on scaling aspects (geometrical (i.e. W & L), power (following Wunsch-Bell power curve) and electrical (rise time)

- 2. Understand how to experimentally extract high current characteristics

- 3. To optimize ESD protection circuits based on fundamental components behavior

# DD231: ESD System Level: Physics, Testing, Debugging of Soft and Hard Failures

On-Demand Tutorial

David Pommerenke, Graz University of Technology

#### **Abstract**

The tutorial is an expanded version of the previous DD231 tutorial on system level ESD. The main difference is the addition of many experimental demonstrations, update of information, and in-depth discussion on problems of the IEC 61000-4-2 testing, with examples on how to perform this testing and obtain the best possible results and documentation. About half of the time will be spent on experimental demonstrations. Topics will include:

- ESD physics: charging and discharging.

- System level ESD testing

- · System level soft failure mechanisms and debugging

- · Design for avoiding ESD problems

### **Learning Outcomes**

The seminar will enable the audience to better understand system level ESD testing such that meaningful, repeatable tests can be performed and data is gathered, that allows to identify the root cause of observed failures.

## TUTORIALS: On-Demand 1 tutorial equals a half day credit

# FC166: ESD QMS Best Practices Strategy Including Class 0 and Costly Controversial ESD Myths

On-Demand Tutorial

Ted Dangelmayer, Dangelmayer Associates, LLC.

#### Abstract

Part I: ESD QMS Best Practices Strategy Including Class 0 While most companies are acutely aware of the hazards of ESD (electrostatic discharge), few are aware that the ESD QMS Strategy is equally important as the technical requirements. This is especially true for the extreme ESD sensitivities of Class 0 since the trend toward Class 0 devices is escalating rapidly. Furthermore, most companies do not know what their device sensitivities are because 90% of IC datasheets do not include CDM Sensitivity data. The absence of this data and the lack of understanding of ESD QMS best practices has reached a critical stage.

S20.20 (ANSI/ESD S20.20) is the best industry standard available and is an excellent foundation for ESD QMS best practices programs. However, companies with advanced technologies have found they must customize the technical requirements of S20.20 and introduce sound ESD QMS practices to avoid unacceptable failure rates in the factory and field. Join us for this interactive presentation and learn if you are at risk and how to establish a robust ESD QMS strategy. You will also learn how to obtain ESD CDM & HBM device sensitivity data as well as how to prepare for Class 0.

Part II: Costly Controversial ESD Myths

There are several common misunderstandings and controversies that can have significant impact on costs, quality and reliability of ESD programs. These misunderstandings or "myths" often result in costly unnecessary expenditures and/or a compromise of the program integrity. These same myths are cited by skeptics who do not fully understand the physics involved. Consequently, it is important to identify and dispel these myths.

Latency is a significant reliability consideration that is surrounded with controversy. Some experts will argue that latency is virtually non-existent while others claim that it is the dominant failure mode. Join us for this highly interactive discussion and learn about Latency as well as common myths such as:

Myth: Circuit Boards are Less Sensitive to ESD than Devices Myth: HBM Data Are Sufficient for Determining Device Sensitivity Levels

Myth: MM Is A Valid Simulation Related To Machines

Myth: Air Flow Causes Charging

Myth: Metalized or Highly Conductive Shielding Layers Are Essential

Myth: Humidity Control is Essential for ESD

Myth: Latency Failures Comprise 90% of ESD Failures

## **Learning Outcomes**

- A Deep Appreciation for The Importance of A Solid ESD QMS Strategy

- How To Include Class 0 In The QMS Strategy

- The Importance of Fully Understanding ESD Fundamentals and Advanced Technology

- How Many ESD Myths Can Disrupt the Best of ESD Programs And How To Prevent This From Happening

- A Review of Important Technical Concepts Such as CDM And CBE

# **NEW** DD208: ESD Parameters for the Foundry, IC Designer and IP/EDA Vendor

On-Demand Tutorial

Efraim Aharoni, Tower Semiconductor

#### **Abstract**

ESD devices and protection circuits should demonstrate an effective shunting and clamping of ESD stress in ICs and electronic systems. It should also not influence the proper functionality of the protected system. The trade-off between ESD capability and signal integrity is reflected in key ESD parameters extracted from dedicated measurements. The ESD protection, planned at IC design level, requires information and data exchange between foundry supplier, IP vendor, and IC designers, and EDA tools vendors. This tutorial aims in guiding the ESD engineer in the foundry in the process of creation and supplying the ESD portion of the PDK. In particular providing a variety of special parameters required for design of an optimized ESD protection. This includes an overview of benchmark key ESD parameters, test structures, measurements, extraction methods, and useful presentation of the information. The designer and the EDA tool vendor are equipped with the know-how of using the parameters in optimizing the ESD window as well as developing effective methods of proper ESD protection, ESD checkers and simulations. As part of this tutorial, two technical reports ESD TR22.0-01-14 (Relevant ESD foundry parameters for seamless ESD design and verification flow) and ESD TR22.0-02-18 (ESD parameters from Intellectual Property (IP) providers), written by ESDA 'ESD parameters' WG-22, are reviewed.

### **Learning Outcomes**

- 1. Learn about the required ESD-related deliverables that the foundry should provide to its design customers and IP/EDA tools vendors. In formal words, the ESD ingredients of the Process Design Kit (PDK).

- 2. Understand the benchmark methods for creation and extraction of ESD-related data, including test-structures, measurement procedures and tools, as well as presentation of key parameters, curves, etc. This know-how covers a variety of technologies ranging from CMOS, RF, embedded NVM, to high voltage BCD.

- 3. Learn about possible monitoring of ESD parameters, protection performance, interference to normal operation, and robustness to process variation.

- 4. Exposure to the inter-relations between the foundry, the IC designer, IP vendors, and EDA tools vendors, from the ESD perspective. In particular, the data exchange between foundry supplier, IP vendor, EDA tool vendor, and IC design integration.

### **TUTORIALS: On-Demand**

# DD220: Transmission Line Pulse (TLP) Basics and Applications

On-Demand Tutorial

Evan Grund, Grund Technical Solutions, Inc.

Certification: DD

#### **Abstract**

This tutorial will cover the basics of TLP including underlying theory, the types of TLP systems available, and how I-V curves are extracted from TLP pulses. The tutorial uses examples to show how fundamental device parameters can be measured with TLP. These parameters allow the ESD engineer to understand a technology's properties which can be used to design successful ESD protection circuits. The student will gain an understanding of the purpose of TLP measurements, how TLP relates to HBM and CDM, fundamentals of how TLP systems work, including impedance and refl ections, types of TLP systems, importance of load lines, adaptive ranging, TLP calibration, time dependence from TLP, and biased TLP measurements. The tutorial will present examples of TLP use for nMOS transistors, diodes, oxides/capacitors, and power supply clamps, as well as time dependent TDR-O and VF-TLP examples.

# DD/FC250: What Information Needs to be Exchanged for Potential EOS Problem

On-Demand Tutorial

Kai Esmark, Infineon Technologies; James Roberts, Stoneridge, Inc.

#### **Abstract**

EOS-like damages represent a significant percentage of components returned by the OEM's to tier1 and semiconductor manufacturers for comprehensive failure analysis in the automotive industry. There is generally a requirement from the OEM to conduct a detailed investigation to determine the root cause of the failure; however, commonly this cannot be done due to missing information and poor communications but blocks a lot of capacity. This tutorial presents information based on case studies why it is not possible to find the root cause for an EOS-like damage without an information sharing between all tier levels. Based on the new guideline a two level support will be introduced based on an information sharing between the OEM, tier1 and semiconductor manufacturers that can lead to a higher chance to identify the root cause of the damage and allows to focus on the important topics.

### **Learning Outcomes**

- Knowledge of basics EOS

- Learning of definitions of EIPD and EOS based on WP4

- Understanding why not all field returns can be treated in the same way

- Introduction of 2 level process for support on potential EOS issues in automotive industry

- Knowledge of typical questions of ANSI SP27.1 for solving these problems

## Technical Sessions: Tuesday, September 15, Parallel Sessions

Exhibitor Showcase 10:15 AM-10:25 AM

Magwel NV

Session 1A: 10:25 AM-12:05 PM

# 1A: Advanced CMOS EOS/ESD and Latchup

Co-Moderators: Scott Ruth, AMD; Markus Mergens, QPX

# **1A.1 Latchup Test Structure Optimization in Advanced CMOS Technologies**

Collin Reiman, Nathan Jack, Intel Corporation

Latchup sensitivity is often measured with a single collinear PNPN test victim. This method is insufficient for measuring the latchup performance of advanced CMOS technology because it does not represent real-world designs. As a result, the predicted latchup performance is too optimistic. In this work, more realistic latchup test structures are discussed. By adopting these new structures, a more accurate prediction of latchup sensitivity can be measured, leading to better latchup prevention.

# 1A.2 ESD Protection Diodes in Sub-5nm Gate-All-Around Nanosheet Technologies

Shih-Hung Chen, Anabela Veloso, Hans Mertens, Geert Hellings, Marko Simicic, Wen-Chieh Chen, Wei-Min Wu, Kateryna Serbulova, Dimitri Linten, Naoto Horiguchi, imec

A Gate-All-Around (GAA) nanosheet (NS) transistor is a candidate for sub-5nm bulk Si CMOS. The impact of the new architecture and relevant process options on intrinsic ESD performance needs to be studied. The first measured results show GAA NS ESD diode performance is strongly influenced by dual epitaxy process options.

# **1A.3 Analytical Model and Verification Algorithm to Prevent Injection Induced Latchup Failures**

David Marreiro, Slavica Malobabic, Vladislav Vashchenko, Maxim Integrated Corp.

Unexpected latchup qualification test failures of HV analog integrated circuit were observed and explained by a new mechanism - injection current upset of internal HV blocks resulting in overload and burnout of LV circuits. A novel verification algorithm is implemented based on analytical model calibrated with latchup test structures data.

# 1A.4 Increased Latch-up Susceptibility of ICs using Reverse Body Bias

Sandeep Vora, Elyse Rosenbaum, University of Illinois at Urbana Champaign; Michael Stockinger, NXP Semiconductors

This work presents a previously undocumented cause of latchup in circuits with reverse body bias capability. This latch-up phenomenon was first noticed during power-on ESD testing. The latch-up risk is determined by the biasing scheme and power delivery network. SPICE simulations are used to confirm the cause and evaluate counter-measures. Exhibitor Showcase: 10:15 AM-10:25 AM

iT2 Technologies,LLC

Session 1B: 10:25 AM-12:05 PM

**1B - Device Testing: Testers, Methods and Correlation Issues I**

Moderator: Brett Carn, Intel Corporation

# **1B.1 Impact of Alternative CDM Methods on HV ESD Protections Behavior**

Leonardo Di Biccari, Andrea Boroni, Alessandro Castelnovo, Lucia Zullino, Lorenzo Cerati, Antonio Andreini, STMicroelectronics; Heinrich Wolf, Johannes Weber, Fraunhofer EMFT

Alternative CDM methods show a good correlation with Field Induced CDM on failing peak current for products not affected by recovery effects. Methods correlation using HV technologies impacted by Forward Recovery Effects, considering multiple DUT impedance variations and rise time impact, is investigated by means of characterizations and TCAD simulations.

# **1B.2 Optimization of Wafer-Level Low-Impedance Contact CDM Testers**

Marko Simicic, Shih-Hung Chen, imec; Wei-Min Wu, imec, KU Leuven, National Chiao Tung University; Nathan Jack, Intel Corp.; Shinichi Tamura, Yohei Shimada, Masanori Sawada, Hanwa Electronic Ind.

The low-impedance contact CDM (LICCDM) ESD tester can be used for wafer-level CDM testing. However, compared to the industry standard field-induced CDM (FI-CDM), it shows some differences. We investigate solutions to mitigate these differences which are mainly the wafer chuck influence and the probe reflections due to matching.

# 1B.3 Charged Device Model (CDM) and Capacitive Coupled Transmission Line Pulsing (CC-TLP) Stress Severity Study on RF IC's

Dolphin Abessolo-Bidzo, Victoria Kiriliouk, Sheela Verwoerd, NXP Semiconductors; Johannes Weber, Heinrich Wolf, Ellen Jirutková, Fraunhofer EMFT

This paper studies the CDM stress severity on RF IC's. The IC's are housed in various IC packages sizes and tested with both CDM and CC-TLP test methods. Empirical correlation factors are established based on peak current and energy content driven failure mechanisms of RF pins.

# 1B.4 A Relay Discharged FI-CDM Method for Improved Repeatability

Matthew Drallmeier, Wei Huang, ESDEMC Technology LLC; David Pommerenke, Graz University of Technology

A new design for CDM testing is proposed that retains the field charging DUT method while providing a consistent discharge inside of a reed switch. The method is shown to adhere to the current JS-002 industry standard and to perform with high repeatability and at low charging voltages.

## Technical Sessions: Tuesday, September 15, Parallel Sessions

Exhibitor Showcase: 1:15 PM-1:25 PM

Estatec, LLC

Session 2A: 1:25 PM-2:15 PM

2A: Numerical Modeling and Electronic Design Automation I

Moderator: Gernot Langguth, Infineon Technologies

# 2A.1 Addressing Latch-up Verification Challenges of 2.5D/3D Technologies

Dina Medhat, Ain Shames University, Mentor, a Siemens Business; Mohamed Dessouky, DiaaEldin Khalil, Ain Shames University

This paper illustrates advanced latch-up verification challenges associated with 2.5D/3D ICs, especially for external and mixed voltage rules. It presents the proposed automated verification flows and demonstrates experimental results. Flows are based on identification of external IOs from the assembly level, without using any layout markers on the die level.

# **2A.2 Empirical ESD Modeling of Multi-Gate ESD Transistors** *Efraim Aharoni, Avi Parvin, TOWERJAZZ*

ESD transistors with multiple parallel gate terminals were measured by TLP using worst-case scenario set-up. Empirical ESD Models for ESD transistors with multiple gates, were created. They employ behavioral code and contain the dependency of Vt1 and post-snapback characteristics on the sizes of the multiple gates of the ESD transistor.

Exhibitor Showcase: 1:15 PM-1:25 PM

**HPPI GmbH**

Session 2B: 1:25 PM-2:15 PM

# 2B: Device Testing: Testers, Methods and Correlation Issues II

Moderator: Robert Gauthier, GLOBALFOUNDRIES

### 2B.1 Pitfalls for Transient Analysis with VF-TLP

Theo Smedes, Sander Sluiter, Paul Cappon, NXP Semiconductors; Mart Coenen, EMCMCC

Analyzing transient ESD device behavior with TLP equipment requires more attention for implementation and measurement details than the classical quasi-static TLP approach. Minimizing hardware parasitics reduces the de-embedding effort and optimizes the quality of the voltage and current measurements. We explore different methods and hardware options and highlight potential pitfalls.

# 2B.2 Transmission Line Pulse (TLP) Statistical Characterization Approach

L. Merlo, L. Di Biccari, A. Castelnovo, L. Cerati, A. Boroni, A. Martino, A. Andreini, STMicroelectronics

In this work a methodology to properly define design guidelines by means of TLP statistical data analysis is presented, avoiding overdesign and failures for products. Using fully automated TLP set-up, a large amount of characterization data is collected. This information can be used to drive an advanced optimization of ESD protections.

## Technical Sessions: Tuesday, September 15, Parallel Sessions

Exhbitor Showcase 3:00 PM-3:10 PM

Session 3A: 3:10 PM-4:00 PM

# 3A: Numerical Modeling and Electronic Design Automation II

Moderator: Gernot Langguth, Infineon Technologies

# **3A.1 Novel ESD Compact Modeling Methodology Using Machine Learning Techniques**

Wei Liang, Xuejiao Yang, Alain Loiseau, Souvick Mitra, Robert Gauthier Jr., GLOBALFOUNDRIES

Novel ESD compact modeling methodology using machine learning techniques is proposed in this paper. Comparisons between conventional, novel fitting methodology and among different machine learning models are discussed. The advantages of this novel methodology are introduced and methods to further improve the model accuracy are also discussed.

#### 3A.2 Efficient ESD Generator Modeling Using Reinforcement Learning

Akhilesh Kumar, En-Cih Yang, Ming-Chih Shih, Ying-Shiun Li, Wen-Tze Chuang, Norman Chang, ANSYS, Inc.

This paper describes Reinforcement Learning (RL) based technique for estimating the parameters of ESD generators modeled using circuit templates, given the current discharge waveform. The proposed algorithms can be applied to any circuit template to tune the circuit parameters for the desired application or optimization efficiently with minimum prior knowledge.

**Exhbitor Showcase 3:00 PM-3:10 PM**

Barth Electronics, Inc.

Session 3B: 3:10 PM-4:25 PM

**3B: Device Testing: Testers, Methods and Correlation Issues III**

Moderator: Robert Gauthier, GLOBALFOUNDRIES

**3B.1** An Experimentally Verified Methodology for Calculating Coaxial Cable Loss Effects on CDM Waveforms Peyman Ensaf, Intel Corp.; Timothy J. Maloney, Center for Analytical Insights

Experimental verification of a turnkey methodology for assessing the precise impact of cable loss on specified CDM pulses in the time domain is presented. Experiments verify the impact of cable losses, mainly skin depth, by convolving CDM waveforms with impulse responses for cables of various lengths.

# **3B.2 Ultrafast RVS as an Efficient Method to Measure Oxide Breakdown in the EOS and ESD Time Domain**

Simon Van Beek, Marko Simicic, Jacopo Franco, Shih-Hung Chen. Dimitri Linten. imec.

Conventional methods to measure breakdown in the ESD time domain, make use of time consuming TLP measurements with a fixed pulse amplitude. With ultrafast RVS, similar equivalent lifetime of oxide breakdown is obtained, using only a pulse generator and oscilloscope and without the need of predefined stress conditions like in CVS.

# **3B.3 Cable Discharge Event Simulation and Measurement Methods**

Pasi Tamminen, EDR&Medeso

Cable discharge events can damage sensitive electronics and these risks can be estimated with measurement and simulation methods. Here measured cable discharges are compared to 3D simulation and vector network analyzer S-parameter based discharge current calculations. This study shows that real-world cable discharge events can be estimated based on calculation methods.

# MANUFACTURING KEYNOTE

**Tuesday, September 15**

9:00 a.m. - 9:45 a.m.

# **ESD Control Program Management for the Factory of Tomorrow**

Kevin Duncan, Seagate Technology

As IC technologies evolve in favor of faster IO speeds and increased package sizes, challenging constraints will be placed on development of on chip ESD protection. Current industry approach uses Human Body Model (HBM) and Charged Device Model (CDM) testing to determine the relative sensitivity of a device to aid the ESD Program Manager in developing and ESD control program plan.

With this information ESD protection strategies and handling risk assessments are conducted and control programs developed. These control programs typically follow general industry guidance and best practices. Few make a conscious and concerted effort to develop a program tailored for their individual needs. Developing this tailored program approach is the next evolutionary step in ESD control program management.

This talk will review current ESD control program management approaches and look at different ways to evaluate ESD threats in your process. Armed with this knowledge we will talk about how ESD control methodologies will change, which controls will require additional focus, and new threats that will need to be considered.

Kevin Duncan currently serves as the Corporate ESD Program Manager for Seagate Technology. In this position he is responsible for controlling factory level ESD in the ultra-sensitive Hard Disc Drive manufacturing process.

Kevin has been a member of the ESD Association since 2000 and is currently the Chairman of the Technical and Administrative Support (TAS) Committee and Vice Chairman of the Standards Committee. He has served as Chairman of Working Group 3 – Ionization and currently as Chairman of WG53, Compliance Verification and serves as a member of many additional Working Groups. He enjoys teaching and has spent many years providing training regarding ESD Control Program Management.

Kevin is a Technical Expert of the United States National Committee, where he represents the United States participating in International Electrotechnical Commission (IEC) Technical Committee 101 – Electrostatics, where he currently serves as Convener of Maintenance Team 9 – Footwear and Flooring and participates in various other Maintenance Teams and Working Groups. He is an ESD Certified Professional Program Manager and an iNARTE Certified ESD Engineer.

## **Technical Sessions: Tuesday, Manufacturing**

# Manufacturing I

10:15 a.m. - 11:30 a.m.

(Moderator: Andy Nold, Teradyne)

## M.1 Shielding Effectiveness of ESD Protective Packaging

John Werner, Piyush Kashyap, John Kinnear, IBM

There has always been the claim that ESD protective packaging will shield electric fields. While there exist tests to measure the shielding effectiveness of materials, there does not exist any measurement on protective packaging. One approach to measuring field shielding is described in this paper where a noise source is placed inside multiple types of ESD protective packages. The ESD protective packaging with the noise source was then placed in a reverberation chamber where radiated emissions measurements were studied.

# M.2 Can Electrostatic Discharge Sensitive Electronic Devices be Damaged by Electrostatic Fields?

Jeremy Smallwood, Electrostatic Solutions Ltd

This paper demonstrates that very high impedance voltage sensitive device such as MOSFETs or MOS capacitors can be damaged due external field changes without making contact with other conductors. A simple electronic model is proposed. A neon bulb is used as proxy for the voltage sensitive device in practical experiments.

### M.3 A Thin Film Storage Device to Characterize the CDM Event Distribution of a Process

Matt Lauderdale, Emmanuel Onyegam, Brad Smith, Jane Yater, NXP Semiconductors; Scott Ruth, AMD

TFS Flash technology is incorporated into chips as a mean to detect, measure, and record CDM events that the chip experiences during processing and handling. TLP and CDM results show a VT shift proportional to the discharge. the VT shift can be tuned and is measured by standard test equipment.

# Technology Showcase I 1:00 p.m. - 1:30 p.m.

(Moderator: Michelle Lam, IBM)

# Flooring Systems from A-Z

Tom Ricciardelli, StaticStop/SelecTech, Inc.

The presentation will cover:

What constitutes a complete ESD flooring system to ensure it provides a reliable grounding mechanism for personnel. The various types of ESD flooring systems available. Unique Interlocking ESD flooring systems that overcome many of the pitfalls associated with conventional ESD flooring systems.

# Technology Showcase II 1:30 p.m. - 2:00 p.m.

(Moderator: Michelle Lam, IBM)

# New Steady-state DC Bar Ionizer Technology Introduction

Joshua Yoo, Core Insight, Inc.

Most bar ionizers are constructed by conventional AC, pulsed AC, or high frequency AC ionizers and they have swing voltage of more than 500 V p-p. Recently, a developed and patented innovative design bipolar nozzle could use steady-state DC bar ionizer which eliminates swing voltage. Conventional DC bar has 300 - 400 V offset voltage at each end of the bar and cannot be used for ESD control in the EPA. Swing voltage from an AC bar ionizer could lead to ESD damage on a device such as ultrasensitive IO pins or class 0 device handling automated process for ESD control applications.

## **Panel Session**

2:25 p.m. - 3:25 p.m.

### Then, Now and Future of ESD control

Moderator: Marcus Koh, Everfeed Technology Pte Ltd

Panelists: Christopher Almeras, Raytheon; Bernard Chin, Qorvo; Rita Fung, Cisco; Matt Jane, Tesla; Dale Parkin Seagate Technology

A panel of ESD control experts in electronics, automobile, space and aviation system will come together to discuss their perspectives in current and future state of ESD control in manufacturing, sharing best practices and lessons learned in implementing ESD control program, training plan, compliance verification and qualification,etc. Bring your questions and pain point, join us in this lively interactive forum.

## Technical Sessions: Wednesday, September 16

# Year-In-Review: Electrical Overstress in Manufacturing and Test

Vladimir Kraz, OnFILTER, Inc.

Wednesday 8:00 AM - 8:40 AM

Electrical overstress (EOS), sometimes referred to as EIPD (electrically-induced physical damage), is a number one cause of damage to devices. This presentation will discuss the recent publication of the technical report (TR) ESD TR23-01-20 - "Identifying, Measuring, and Mitigation of Electrical Overstress Sources". The TR's purpose is to present to a wide constituency of EOS/ESD Association members and adjacent industries a body of knowledge encompassing practical aspects of dealing with EOS in manufacturing environment. The TR describes the basic difference between ESD and EOS and outlines EOS effect on equipment. It further provides explanation on the types and causes of EOS in manufacturing. An important portion of the TR is dedicated to EOS measurements and mitigation.

### Exhbitor Showcase 9:10 AM-9:20AM

### Simco-lon

Session 4A: 9:20 AM-10:10 AM 4A: EOS/ESD Failure Analysis,

# **Troubleshooting, and Case Studies II**

Moderator: Alain Loiseau. GLOBALFOUNDRIES

4A.1 Balancing the Tradeoff Between Performance and Mis-Trigger Immunity in Active Feedback-Based High-**Voltage Tolerant Power Clamps**

Alex Ayling, Elyse Rosenbaum, University of Illinois at Urbana-Champaign; Javier Salcedo, Srivatsan Parthasarathy, Jean-Jacques Hajjar, Analog Devices, Inc.