# **Fundamentals of Electrostatic Discharge**

## Part Five - Device Sensitivity and Testing

© 2020, ESD Association, Rome, NY

In Part Two of this series ("Principles of ESD Control – ESD Control Program Development"), we indicated that a key element in a successful static control program is the identification of the most sensitive or ESD susceptible (ESDS) item you are using and what is the withstand voltage classification of the products that you are manufacturing and shipping. Susceptibility of an ESDS item to an ESD event is determined by the device's ability to dissipate or shunt the energy of the discharge or withstand the current and voltage levels involved. Although energy or (peak) current are the most important parameters, the ESD sensitivity or ESD susceptibility is typically classified by withstand voltage. The withstand voltage is defined by the voltage, which causes the discharge, not the voltage, which can be measured at the ESDS item. Part Two included:

• Define the level of control needed in your environment. What is the most sensitive or ESD susceptible (ESDS) item you are using, and what is the withstand voltage classification of the products that you are manufacturing and shipping? To get an idea of what is required, it is best to know the Human-Body Model (HBM) and Charged-Device Model (CDM) sensitivity levels for all devices that will be handled in your facility. ANSI/ESD S20.20 and IEC 61350-5-1 define control program requirements for items that are sensitive to 100 volts HBM and 200 volts CDM. With proper documentation and objective evidence, both standards allow the requirements to be tailored as appropriate for specific situations.

Some devices may be more readily damaged by discharges occurring within automated equipment, while others may be more prone to damage from handling by personnel. In Part Five, we will cover the models and test procedures used to characterize, determine, and classify the sensitivity of items to ESD. Today, these test procedures are based on the two primary models of ESD events: Human Body Model (HBM) and Charged Device Model (CDM). The models used to perform component testing cannot replicate the full spectrum of all possible ESD events, and there is no direct correlation between discharges in the field and in a test system. Nevertheless, these models have been proven to be successful in reproducing over 99% of all ESD field failure signatures, and typically, the ESD withstand voltages obtained by models in test systems are worst-case compared to real-world events with the same discharge voltage. With the use of standardized test procedures, the industry can:

Develop and measure suitable on-chip protection.

- Enable comparisons to be made between devices.

- Provide a system of ESD sensitivity classification to assist in the ESD design and monitoring requirements of the manufacturing and assembly environments.

- Have documented test procedures to ensure reliable and repeatable results.

### **HUMAN BODY MODEL (HBM) TESTING**

One of the most common causes of ESD damage is the direct transfer of electrostatic charge from the human body or from a charged material to the ESDS item. When one walks across a floor, an electrostatic charge accumulates on the body. Simple contact (or even close proximity) of a finger to the leads of an ESDS item allows the body to discharge, possibly causing device damage. The model used to simulate this event is the Human Body Model (HBM).

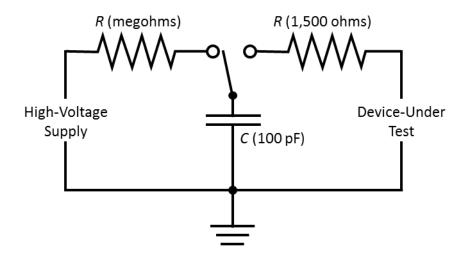

The Human Body Model is the oldest and most commonly used model for classifying device sensitivity to ESD. The HBM testing model represents the discharge from the fingertip of a standing individual delivered to the device. It is modeled by a 100 pF capacitor, which is charged by a high-voltage supply through a high-ohmic resistor (typically in the megohm regime) and then discharged through a switching component and a 1.5 k $\Omega$  (1,500 ohms) series resistor through the component to ground or to a lower potential. This model, which dates from the nineteenth century, was developed for investigating explosions of gas mixtures in mines. It was adopted by the military in MIL-STD-883 Method 3015 and is referenced in ANSI/ESDA/JEDEC JS-001: Electrostatic Discharge Sensitivity Testing — Human Body Model (HBM) Component Level. This document replaces the previous ESDA and JEDEC methods, STM5.1-2007 and JESD22-A114F, respectively. The simplified Human Body Model circuit without any parasitics from the test system is presented in Figure 1.

Figure 1: Typical (simplified) Human Body Model Circuit

A typical HBM waveform has a rise time of 2–10 ns, a peak current of 0.67 amps/kilovolts, and a double-exponential decay with a width of 200 ns. Typically, the decisive parameter which causes the failure is the energy of the HBM pulse.

Testing for HBM ESD susceptibility is typically performed using automated test systems. The device is placed in the test system and contacted through a relay matrix. One pin is connected to the HBM network ("zap pin"), and one or several other pins are connected to tester ground ("ground pins"). With today's high-pin count devices, a full test of all possible stress combinations is no longer possible, thus pin combinations have to be selected, which guarantees sufficient coverage to detect weak stress combinations. These pin combinations which must be stressed are defined in the current HBM standard. Electrostatic discharges (ESD) are applied with a waveform generated by a Human Body Model network. A device is determined to have failed if it does not meet the datasheet parameters using parametric and functional testing.

One has to state clearly that the Human Body Model, according to JS-001 addresses handling issues. Sometimes, the well-known IEC 61000-4-2 is also called "Human Body Model," but that model addresses ESD events in a system under different operating conditions and, therefore, should be applied to systems only. The waveform and the severity of the IEC 61000-4-2 and the JS-001 cannot be compared. For handling issues, only JS-001 is meaningful.

### CHARGED DEVICE MODEL (CDM) TESTING

The transfer of charge *from* an ESDS item to a conductive surface at a lower potential is also an ESD event. A device may become charged, for example, from sliding down the part feeder in automated handling equipment. If it then contacts the insertion head or another conductive surface, which is at a lower potential, a rapid discharge may occur from the device to the conductive surface. This discharge event is known as the Charged Device Model (CDM) event and can be more damaging than the HBM for some devices. Although the duration of the discharge is very short – often less than one nanosecond – the peak current can reach several tens of amperes, causing significant voltage drops in the device and eventually resulting in breakdown of dielectrics (e.g., gate oxides) due to the excessive current.

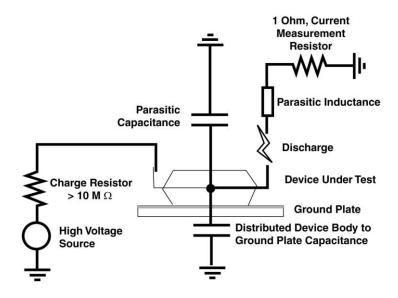

The device testing standard for CDM is ANSI/ESDA/JEDEC JS-002: *Electrostatic Discharge Sensitivity Testing – Charged Device Model (CDM) Device Level.* This document replaces the previous ESDA and JEDEC methods, STM5.3.1 and JESD22-C101, respectively. The test procedure involves placing the device on a field plate with its leads pointing up, then charging it, and discharging the device. All pins are treated equally and are discharged after positive and negative charging. Figure 2 illustrates a simplified CDM test circuit with direct charging of the device.

Figure 2: Typical Charged Device Model Test

## OTHER TEST METHODS

# Machine Model (MM) Testing

Over the years, the industry shifted away from MM as a qualification test and moved towards using the qualification documents of ANSI/ESDA/JEDEC JS-001 (HBM) and ANSI/ESDA/JEDEC JS-002 (CDM) to fully characterize a component's ESD susceptibility. A discharge can occur from an isolated conductor, or a charged conductive object, such as a metallic tool, or an automatic equipment or fixture, therefore the CDM method simulates metal to metal discharges better.

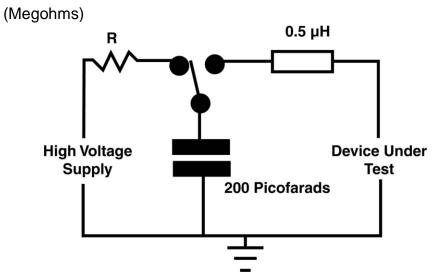

Originating in Japan as the result of trying to create a worst-case HBM event, the model is known as the Machine Model. This ESD model consists of a 200 pF capacitor discharged directly into a component with no series DC resistor in the output circuitry. The discharge waveform can be oscillating with the rise time and pulse width, similar to HBM. The Machine Model typically addresses the same physical failure mode as the Human Body Model, therefore, it is useful when determining failure mode and producing HBM-like ESD effects at significant lower levels.

Testing of devices for MM sensitivity using *ESD SP5.2: Electrostatic Discharge Sensitivity Testing – Machine Model (MM) Component Level* is similar in procedure to HBM testing. The basic test equipment and the stress combinations are the same, but the test head is very different. The MM version does not have a 1,500 ohm resistor, but otherwise, the test board and the socket are often the same as for HBM testing. The series inductance, as shown in Figure 3, is the dominating parasitic element that shapes the oscillating machine model wave form. The series inductance is indirectly defined through the specification of various waveform parameters like peak currents, rise times, and the period of the waveform. However, the inductance is not well defined. Hence, for different testers, the MM withstand voltage might differ by at least a factor of 2–5, although both test systems comply with the current standard. The lack of reproducibility of test results and the fact that the well reproducible HBM addresses the same failure

mode as HBM are the main reasons that the industry shifted away from MM qualification. JEDEC and ESDA do not recommend to qualify products with Machine Model, but qualifying with HBM and CDM instead. Furthermore, the Machine Model risk is now referred to as Isolated Conductor risk mitigation in the ANSI/ESD S20.20. Machine Model testing of integrated circuits (ICs) should be limited to failure analysis without correlation of withstand voltages and charging in the field.

Figure 3: Typical Machine Model Circuit

### DEVICE SENSITIVITY CLASSIFICATION

The HBM and CDM methods include a classification system for defining the component sensitivity to the specified model (See Tables 1 and 2). These classification systems have a number of advantages. They allow easy grouping and comparing of components according to their ESD sensitivity, and the classification gives you an indication of the level of ESD protection that is required for the component.

Table 1: ANSI/ESDA/JEDEC JS-001 Table 3: HBM ESD Component Classification Levels

| Classification | Voltage Range (V) |

|----------------|-------------------|

| 0Z             | < 50              |

| 0A             | 50 to < 125       |

| 0B             | 125 to < 250      |

| 1A             | 250 to < 500      |

| 1B             | 500 to < 1000     |

| 1C             | 1000 to < 2000    |

| 2  | 2000 to < 4000 |

|----|----------------|

| 3A | 4000 to < 8000 |

| 3B | ≥ 8000         |

Table 2: ANSI/ESDA/JEDEC JS-002 Table 3: CDM ESD Component Classification Levels

| Classification | Voltage Range (V) |

|----------------|-------------------|

| COA            | < 125             |

| COB            | 125 to < 250      |

| C1             | 250 to < 500      |

| C2A            | 500 to <750       |

| C2B            | 750 to < 1000     |

| C3             | ≥ 1000            |

The current HBM and standards divide the Class 0 classification into three withstand voltage levels with class 0Z being less than 50 volt sensitivity, 0A being 50 volts to less than 125 volts, and class 0B being 125 volts to less than 250 volts.

If handling class 0Z and/or 0A items, or sensitivities less than 125 volts, program improvements are called for. To control the environment to decrease the probability of ESD damage in class 0Z or 0A situations involves increasing ESD protective redundancies by adding ESD control items in the EPA and ensuring that they are working properly by increasing the frequency of compliance verifications of those ESD control items perhaps to more stringent required limits.

An ESDS item should be classified using both the Human Body Model and the Charged Device Model. This would alert a potential user of the ESDS item to the need for a controlled environment, whether assembly and manufacturing operations are performed by human beings or automatic machinery.

A word of caution is that these classification systems and component sensitivity test results function as guides, not necessarily as absolutes. The events defined by the test data produce narrowly restrictive data that must be carefully considered and judiciously used. The two ESD models represent discrete points used in an attempt to characterize ESD vulnerability. The data points are informative and useful, but to arbitrarily extrapolate the data into a real-world scenario can be misleading. The true utility of the data is in comparing one device with another and to provide a starting point for developing your ESD Control Programs.

### **SUMMARY**

Device failure models and device test methods define the ESD susceptibility of the electronic devices and assemblies to be protected from the effects of ESD. With this key information, you can design more effective ESD Control Programs. However, do expect devices to become more susceptible. The ESD Association's White Paper "Electrostatic Discharge (ESD) Technology Roadmap — Revised April 2010" includes "With devices becoming more sensitive through 2010-2015 and beyond, it is imperative that companies begin to scrutinize the ESD capabilities of their handling processes. Factory ESD control is expected to play an ever-increasing critical role as the industry is flooded with even more HBM (Human Body Model) and CDM (Charged Device Model) sensitive designs. For people handling ESDS items, personnel grounding systems must be designed to limit body voltages to less than 100 volts." Users should refer to the most recent update by the Industry Council for guidance.

#### FOR FURTHER REFERENCE

ANSI/ESDA/JEDEC JS-001 *Electrostatic Discharge Sensitivity Testing – Human Body Model*, ESD Association, Rome, NY.

ESD SP5.2: Electrostatic Discharge Sensitivity Testing – Machine Model, ESD Association, Rome, NY.

ANSI/ESDA/JEDEC JS-002 *Electrostatic Discharge Sensitivity Testing – Charged Device Model*, ESD Association, Rome, NY.

ANSI/ESD S20.20 Standard for the Development of an ESD Control Program, ESD Association, Rome, NY

ESD Industry Council White Paper 1: "A Case for Lowering Component Level HBM/MM ESD Specifications and Requirements," August 2008, and ESD Association's White Paper "Electrostatic Discharge (ESD) Technology Roadmap — Revised April 2010 http://www.esda.org/IndustryCouncil.html.

ESD Industry Council White Paper 2: "A Case for Lowering Component Level CDM ESD Specifications and Requirements," March 2009, <a href="http://www.esda.org/IndustryCouncil.html">http://www.esda.org/IndustryCouncil.html</a>.

"Process ESD Capability Measurements," Steinman, Arnold, EOS/ESD Symposium Proceedings, 2012, p. 211, ESD Association, Rome, NY.

"Is there a Correlation Between ESD Qualification Values and the Voltages Measured in the Field?", Gaertner, Reinhold, and Stadler, Wolfgang, EOS/ESD Symposium Proceedings, 2012, p. 198, ESD Association, Rome, NY.

"A Closer Look at the Human ESD Event," Hyatt, Hugh, et al., EOS/ESD Symposium Proceedings, 1981, ESD Association, Rome, NY.

"Charged Device Model Testing: Trying to Duplicate Reality," Avery, L.R., EOS/ESD Symposium Proceedings, 1987, ESD Association, Rome, NY.

"Critical Issues Regarding ESD Sensitivity Classification Testing," Pierce, Donald C., EOS/ESD Symposium Proceedings, 1987, ESD Association, Rome, NY.

- "Beyond MIL HBM Testing How to Evaluate the Real Capability of Protection Structures, Avery, L.R., *EOS/ESD Symposium Proceedings*, 1991, ESD Association, Rome, NY.

- "Mechanisms of Charged-Device Electrostatic Discharges," Renninger, Robert G., EOS/ESD Symposium Proceedings, 1991, ESD Association, Rome, NY.

- "Analysis of HBM ESD Testers and Specifications Using a 4<sup>th</sup> Order Lumped Element Model," Verhaege, Koen, et al., *EOS/ESD Symposium Proceedings*, 1993, ESD Association, Rome, NY.

- "A Comparison of Electrostatic Discharge Models and Failure Signatures for CMOS Integrated Circuit Devices," Kelly, M., et al., *EOS/ESD Symposium Proceedings*, 1995, ESD Association, Rome, NY.

- "Study of ESD Evaluation Methods for Charged Device Model," Wada, Tetsuaki, EOS/ESD Symposium Proceedings, 1995, ESD Association, Rome, NY.

- "A Compact Model for the Grounded-Gate nMOS Behavior Under CDM ESD Stress," Russ, Christian, et al., *EOS/ESD Symposium Proceedings*, 1996, ESD Association, Rome, NY.

- "Recommendations to Further Improvements of HBM ESD Component Level Test Specifications," Verhaege, Koen, et al., *EOS/ESD Symposium Proceedings*, 1996, ESD Association, Rome, NY.

- "Very Fast Transmission Line Pulsing of Integrated Structures and the Charged Device Model," Gieser, H., and Haunschild, M., *EOS/ESD Symposium Proceedings*, 1996, ESD Association, Rome, NY.

- "Investigation into Socketed CDM (SDM) Tester Parasitics," Chaine, M., et al., EOS/ESD Symposium Proceedings, 1998, ESD Association, Rome, NY.

- "Issues Concerning CDM ESD Verification Modules-The Need to Move to Alumina," Henry, L.G. et al, *EOS/ESD Symposium Proceedings*, 1999, ESD Association, Rome, NY.

- "The Importance of Standardizing CDM ESD Test Head Parameters to Obtain Data Correlation," Henry, L.G., et al., *EOS/ESD Symposium Proceedings*, 2000, ESD Association, Rome, NY.

- "Component Level ESD Testing," Review Paper, Verhaege, Koen, *Microelectronics Reliability Journal*, 1998.